first shift, then read) - inputs: - ctrl : to load-data and shift operations (right and left shift) - data : it is the data to be shifted - q_reg : store the outputs library ieee use ieee.std_logic_1164.

#Vhdl parallel to serial converter serial#

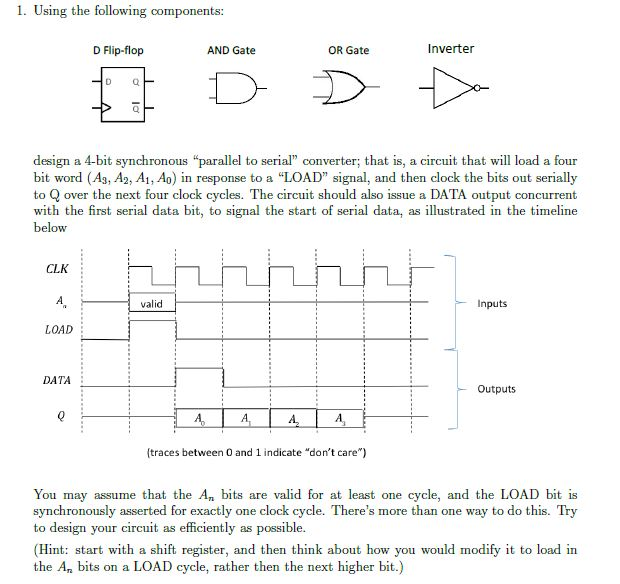

first load, then shift) - serial to parallel conversion (i.e. shift_register.vhd - created by : Meher Krishna Patel - date : 22-Dec-16 - Functionality: - load data and shift it data to left and right - parallel to serial conversion (i.e. Then shifted to right after first cursor and later to the left i.e. 11.3 shows the shifting operation performed by the listing. q_reg(0) for right shift or q(N-1) for left shift whereas for serial to parallel conversion, complete ‘q_reg’ should be read.įig. For, parallel to serial converter, use ony one pin of ‘q_reg’ i.e. Lastly, data is available on the output port ‘q_reg’ from Line 55. But this will affect the working of parallel to serial converter, as we will set ctrl to ‘‘11’‘, when all the data is shifted, therefore all the register which were filled by values from last port, will be overwritten by the new parallel data.

data(N-1) for right shift or data(0) for left shift) during shifting which is actually designed for serial to parallel converter. Note that, in this case, last bit propagates (i.e. Similarly, for parallel to serial converter, first load the data using ctrl=’‘11’‘ and then perform the shift operation until all the bits are read and then again load the data.

#Vhdl parallel to serial converter full#

when all the bits are shifted and register is full then set ctrl to ‘‘00’’ and read the data, after that set ctrl to ‘‘01’’ or ‘‘10’’ for getting next set of bits. It can be used for serial to parallel conversion i.e. Next, ctrl=’‘00’’ is provided for reading the data. (data(N-1)) whereas for left shift (Line 49) data is provided from first port i.e. Note that, to perform right shift (Line 47), data is continuously provided from last port i.e. Lines 41-53 performs various operations based on ‘ctrl’ values. Lines 32-39 clear the shift register during reset operation, otherwise go to the next state. In the listing, the ‘ctrl’ port is used for ‘shifting’, ‘loading’ and ‘reading’ data operation. r_reg ( 0 ) '0' ) - other bits are 0 elsif ( clk 'event and clk = '1' ) then r_reg <= r_next - otherwise save the next state end if end process - N = 3 - Feedback polynomial : x^3 + x^2 + 1 - total sequences (maximum) : 2^3 - 1 = 7 feedback_value <= r_reg ( 3 ) xor r_reg ( 2 ) xor r_reg ( 0 ) - N = 4 - feedback_value <= r_reg(4) xor r_reg(3) xor r_reg(0) - N = 5, maximum length = 28 (not 31) - feedback_value <= r_reg(5) xor r_reg(3) xor r_reg(0) - N = 9 - feedback_value <= r_reg(9) xor r_reg(5) xor r_reg(0) r_next <= feedback_value & r_reg ( N downto 1 ) q <= r_reg end arch random number ) end rand_num_generator architecture arch of rand_num_generator is signal r_reg, r_next : std_logic_vector ( N downto 0 ) signal feedback_value : std_logic - based on feedback polynomial begin process ( clk, reset ) begin if ( reset = '1' ) then - set initial value to '1'. all entity rand_num_generator is generic ( N : integer := 3 ) port ( clk, reset : in std_logic q : out std_logic_vector ( N downto 0 ) - output of LFSR i.e. change 'feedback_value' pattern library ieee use ieee.std_logic_1164. rand_num_generator.vhd - created by : Meher Krishna Patel - date : 22-Dec-16 - Feedback polynomial : x^3 + x^2 + 1 - maximum length : 2^3 - 1 = 7 - if generic value is changed, - then choose the correct Feedback polynomial i.e. But, if we initialize the system with ‘3’ (which is not the set), then the generate sequences will be entirely different.

11.1, the generated sequence contains ‘8, C, 6, B, 5, 2 and 1’ and if we initialize the system with any of these values, outputs will contain same set of numbers again. Further, q values are represented in ‘hexadecimal format’ which are same as r_reg values in ‘binary format’. Here, we can see that total 7 different numbers are generated by LFSR, which can be seen between two cursors in the figure. Lastly, the value r_reg is avalaible to output port from Line 53. In next clock cycle, value of r_next is assigned to r_reg through Line 34. LFSR polynomial are written as \($ bit is feed with ‘feedback_value’ and stored in ‘r_next’ signal. large number of initial values are possible), then the generated numbers can be considered as random numbers for practical purposes. The sequences of random number can be predicted if the initial value is known. These random numbers are generated based on initial values to LFSR. Long LFSR can be used as ‘ pseudo-random number generator’.

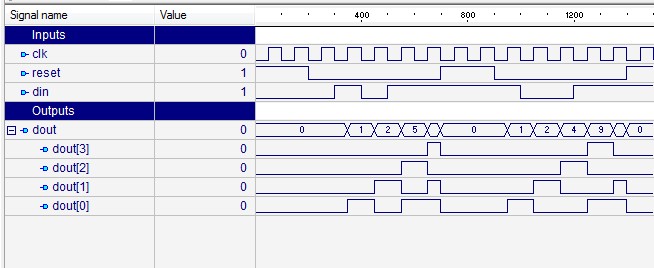

Script execution in Quartus and Modelsimġ1.2.1. Visual test : display different colors on screen Visual test : change screen color with switches ROM implementation logic cells (distributed ROM) Visual test for serial and parallel converters

Top level connection between serial and parallel converters